Home »

» Microcontrollers - 8051 Interrupts

23:25:00

Interrupts are the events that temporarily suspend the main program,

pass the control to the external sources and execute their task. It then

passes the control to the main program where it had left off.

8051 has 5 interrupt signals, i.e. INT0, TFO, INTR1, TF1, RI/TI. Each

interrupt can be enabled or disabled by setting bits of the IE register

and the whole interrupt system can be disabled by clearing the EA bit

of the same register.

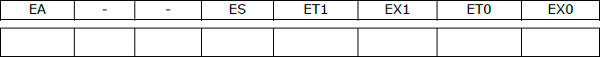

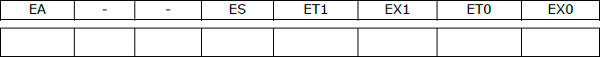

IE (Interrupt Enable) Register

This register is responsible for enabling and disabling the

interrupt. EA register is set to one for enabling interrupts and set to 0

for disabling the interrupts. Its bit sequence and their meanings are

shown in the following figure.

| EA |

IE.7 |

It disables all interrupts. When EA = 0 no interrupt will be acknowledged and EA = 1 enables the interrupt individually. |

| - |

IE.6 |

Reserved for future use. |

| - |

IE.5 |

Reserved for future use. |

| ES |

IE.4 |

Enables/disables serial port interrupt. |

| ET1 |

IE.3 |

Enables/disables timer1 overflow interrupt. |

| EX1 |

IE.2 |

Enables/disables external interrupt1. |

| ET0 |

IE.1 |

Enables/disables timer0 overflow interrupt. |

| EX0 |

IE.0 |

Enables/disables external interrupt0. |

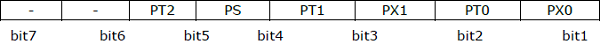

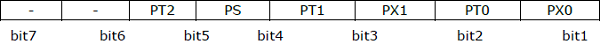

IP (Interrupt Priority) Register

We can change the priority levels of the interrupts by changing the

corresponding bit in the Interrupt Priority (IP) register as shown in

the following figure.

- A low priority interrupt can only be interrupted by the high

priority interrupt, but not interrupted by another low priority

interrupt.

- If two interrupts of different priority levels are received simultaneously, the request of higher priority level is served.

- If the requests of the same priority levels are received

simultaneously, then the internal polling sequence determines which

request is to be serviced.

| - |

IP.6 |

Reserved for future use. |

| - |

IP.5 |

Reserved for future use. |

| PS |

IP.4 |

It defines the serial port interrupt priority level. |

| PT1 |

IP.3 |

It defines the timer interrupt of 1 priority. |

| PX1 |

IP.2 |

It defines the external interrupt priority level. |

| PT0 |

IP.1 |

It defines the timer0 interrupt priority level. |

| PX0 |

IP.0 |

It defines the external interrupt of 0 priority level. |

TCON Register

TCON register specifies the type of external interrupt to the microcontroller.

0 comments:

Post a Comment